-

Computer System OverviewCS/OS 2024. 2. 26. 16:05

Basic Element

Overview of the Operating System Processor

- Arithmetic / Logic Unit (ALU) : performs mathematical calculations and makes logical comparisons

- Central Process Unit (CPU) : a hardware component that performs an instruction set utilizing the ALU, control unit, and registers

- Graphical Process Unit (GPU) : provide efficient computation on arrays of data using Single-Instruction Multiple Data (SIMD) techniques

- SoC : components such as DSPs, GPUs, codecs and main memory, in addition to the CPUs and caches, are on the same chip

Memory

Hierarchy of the memory - 6 transistor = 1 bit Flip-Flop, 8 F/F = 1 byte Register, 64k Reigster = 64KB SRAM

- Static Random Access Memory (SRAM); Cache

- High speed, no refresh required

- Poor density (6 transistors / bit), Expensive

- Dynamic Random Access Memory (DRAM)

- High density

- Slower than SRAM

- Hard Disk Drive

- 비휘발성, 대용량

- 진동에 취약, 속도가 느림

- Flash Memory

- 읽기 시간과 쓰기 시간이 다름; 비대칭성

- 비휘발성, Hard Disk Drive보다 빠름, 진동에 강함

- 덮어쓰기 불가능, 지우는 시간 추가, 비쌈

Processor Register

General Purpose Registers

- Enable programmer to minimize main-memory references

- Register file (bank) : contains all the general purpose registers of the processor

Special Purpose Registers

- Program Counter (PC) : contains the address of an instruction to be fetched

- Instruction Register (IR) : contains the instruction most recently fetched

- Program Status Word (PSW) : contains status information (privilege states, condition code)

- Memory Address Register (MAR) : holds the address of the current instruction that is to be fetched from memory

- Memory Buffer Register (MBR) : holds the contents found at the address held in the MAR

Instruction

Instruction Architecture

- Abstract Data Type (ADT) 추상 데이터 타입 : 자료들의 상태와 연산들을 명시

- State 상태 : Registers + Memory

- Operation 연산 : Set of instructions

- Instruction Format : machine-specific template that specifies

- Length of the op code

- Number of operands

- Length of operands

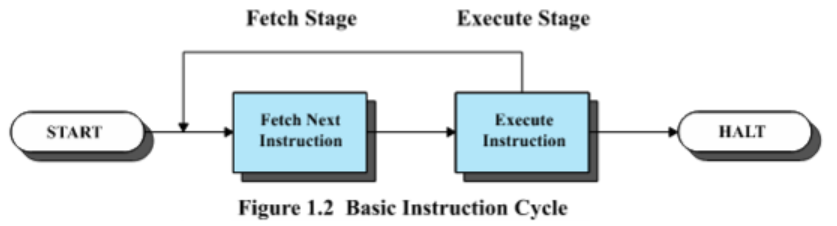

Instruction Execution

- Program : consists of a set of instructions and data

- Instruction Fetch

- Instruction Decode and Execute : processor interprets the instruction and performs required action

- Instruction Cycle

- Fetch instruction from memory : PC - MAR - Memory - MBR - IR

- Decode instruction

- Execute instruction (get other operands if necessary)

- Store result

Interrupts

Interrupt Mechnism

- Provided to improve processor utilization

- Most I/O devices are slower than the processor

- processor must pause to wait for device

- wasteful use of the processor

Interrupts Processing

- Save PC, PSW onto control stack (memory)

- Set PSW to kernel mode and interrupt disable

- Assign interrupt handler to PC

- Save remainder of process state information

- Call Interrupt Service Routine (ISR; device speicific operation)

- Restore process state information

- Call saved PC, PSW

Interrupt Service Routine (ISR)

- Interrupt Descriptor Table (IDT) : 프로세서가 인터럽트와 예외에 대한 정확한 반응을 결정하기 위해 사용

- Status, Handler, Lock, Action으로 구성된 구조체들의 벡터 테이블

- Action : 각 인터럽트에 대한 실제 ISR 코드

- Must execute very quickly

- Example of ISR

asmlinkage unsigned int do_IRQ(struct pt_regs regs) { int irq = regs.orig_eas & 0xff; irq_desc_t *desc = irq_desc + irq; struct irqaction *action = NULL; .... action = desc->action; .... action_ret = handle_IRQ_event(irq, ®s, action); }Interrupts and Exception

- Interrupt (External Interrupt) : interrupt generated by other H/W devices (Asynchronous interrupt)

- Exception (Trap; Software Interrupt) : interrupt generated by the CPU (Synchronous interrupt)

- Interrupts and Exceptions are handled in the same way at Linux

Multiple Interrupts

- Sequential Interrupt Processing

- Disable interrupts while an interrupt is being processed

- Processor ignores any new interrupt request signal

- Drawback : ignore priority or time-critical needs

- Nested Interrupt Processing

- Define priorities for interrupts

- Allow an interrupt of higher priority while doing a lower-priority ISR

- Drawback : expensive (stack structure, demand priorities of interrupts)

Advanced PIC (APIC) for Symmetric Multiprocessing (SMP)

- Programmable Interrupt Controller (PIC)

- I/O devices have Interrupt Request (IRQ) lines

- IRQs are mapped by special hardware to interrupt vectors, and passed to the CPU

- PIC translates device's request to vector

- Possible to "mask" interrupts at PIC or CPU

- Advanced PIC (APIC) : selects a CPU and Delivers signal to corresponding local APIC

- Local APIC (LAPIC)

- One per each CPU in SMP

- Timer interrupt

- All local APICs are connected to external APIC

Memory Hierarchy

Memory Demand Criteria

- Speed

- Cost

- Capacity

Memory Hierarchy

- Goal : to provide a "virtual" memory technology

- The highest-level memory with size

- Cost of the lowest-level memory

- Locality

- Temporal locality (locality in time)

- Spatial locality (locality in space)

- Hit

- Hit rate : fraction of accesses found in upper level

- Hit time : time to access the upper level

- Miss

- Accessed data found only in lower level

- Miss rate = 1 - (Hit Rate)

- Average Access Time : Hit time + miss rate * miss panalty (DRAM access time)

Cache Memory

Cache

- To provide a "virtual" memory technology that has an access time of SRAM (upper level) with the size and cost of DRAM (lower level)

- Reduction of memory bandwidth

- More memory bandwidth for I/O

- No need to change the ISA

- Cache Line

- Tag : memory와 cache 간의 mapping

- Data : cache가 가지고 있는 데이터

- Valid bit : miss일 경우 0으로 표시

- Dirty bit : write 동작 시 memory와 consistency가 유지되지 않은 상태 표시

- Address의 구성 요소

- Index : cache 내 각 cache line의 주소

- Offset : cache line 내 각 word, byte의 주소

Cache Organization

- Direct mapped cache (1-way set associative cache)

- N-way set associative cache

- Fully associative cache

Cache Read

Cache Write

- Write-through

- Write the data into both the cache and main memory

- Simple but slow and increases memory traffic (requires a write buffer)

- Write-back (delayed write)

- Write the data into cache only

- Update the main memory when a dirty block is replaced (requires a dirty bit)

- Fast but complex to implement

- Cause a consistency problem

I/O Communication Techniques

I/O Communication Techniques

- I/O instructions control devices; I/O device controller (hardware)

- I/O device driver (software) : control by register (port register; data-in, data-out, status, control)

- Device have address, used by

- Port I/O (I/O instructions) : 별도의 주소를 사용하므로 별도의 instruction 필요, 추가적인 instruction 사용 가능

- Memory-mapped I/O : 기존의 instruction 사용, ISA 수정없이 사용 가능

Programmed I/O (Polling I/O)

- Processor periodically checks the status of I/O module until the I/O operation is complete

- Reasonable if device is fast

- Inefficient if device is slow (Busy-wait)

- If CPU switches to another task, data may be lost

Interrupt-Driven I/O

- Processor is interrupted when I/O module ready to exchange data

- A lot of interrupt of heavy process (big overhead)

Direct Memory Access (DMA)

- Bypasses CPU to transfer data directly between I/O device and memory

- DMA command block

- Source and destination addresses

- Read or write mode

- Count of bytes

- 동작 모드

- Burst mode : CPU에게 시스템 버스 접근 제어권을 돌려주기 전까지 데이터 블록의 모든 데이터를 전송

- Cycle stealing mode : Bus Mastering을 통해 지속적으로 시스템 제어권을 얻고 해제, Burst mode만큼 빠르진 않지만 길게 대기하지 않음

- Transparent mode : CPU가 시스템 버스를 사용하지 않는 명령을 실행할 때만 데이터를 전송, CPU가 프로그램 실행 도중 멈추지 않고 DMA 전송이 시간 측면에서 자유로우나 구현하기 복잡함

'CS > OS' 카테고리의 다른 글

Threads (0) 2024.04.17 Process Scheduling 2 (0) 2024.03.20 Process Scheduling 1 (0) 2024.03.13 Process Description and Control (0) 2024.03.06 User Program and System Call (0) 2024.03.06